#### **Sound Open Firmware**

#### Liam Girdwood

Open Source Summit + Embedded Linux Conference Europe 2018

Sound Open Firmware is an open source audio digital signal processing firmware and driver infrastructure.

### **SOF Goals 1**

- DSP architecture and platform agnostic.

- Separate architecture and platform code like Linux\*.

- Abstract interfaces for architecture APIs (again like Linux).

- Host AP architecture and host AP OS agnostic.

- Drivers are generic and not coupled to any host architecture.

- Nothing in SOF that couples firmware or low level driver to any OS.

- Toolchain freedom

- Fully support open source tools GCC, Octave, M4, Qemu.

- Also support proprietary tools Cadence xcc and emulator, Matlab.

- Permissive licensing of all firmware and most SDK code.

#### **SOF Goals 2**

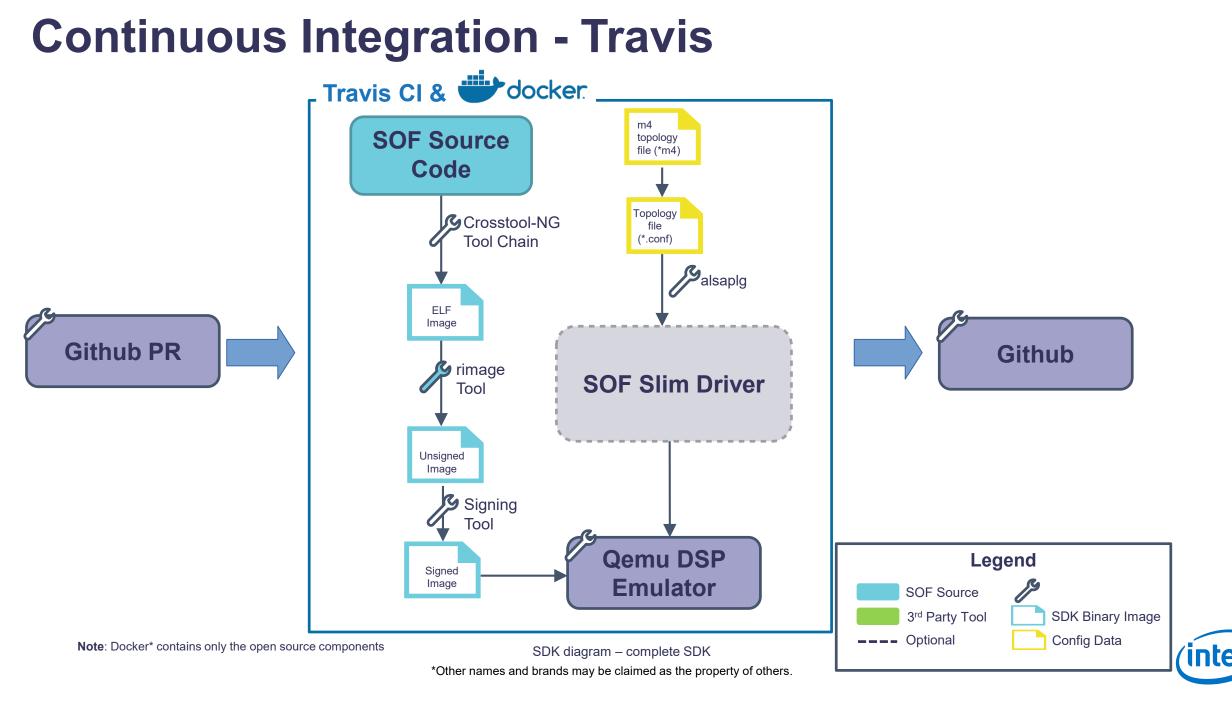

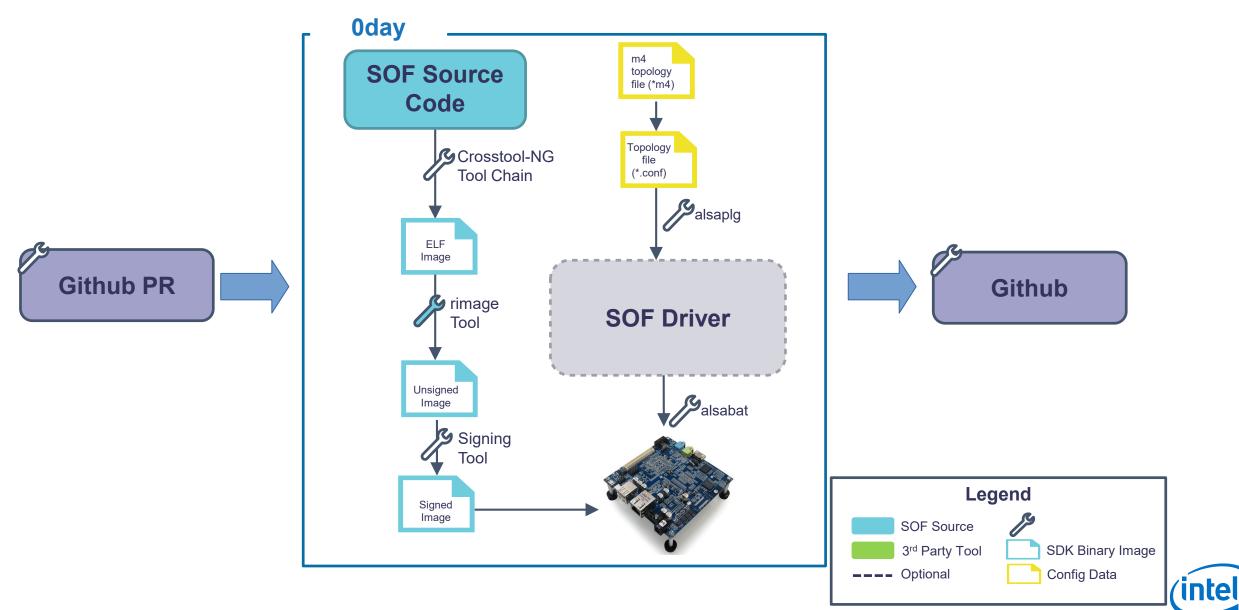

- Freedom for users to define new audio processing pipelines using open source components and tools.

- Freedom for users to develop and integrate proprietary audio processing algorithms.

- All development done in public.

- Support for several CI systems to best match device and infrastructure under test.

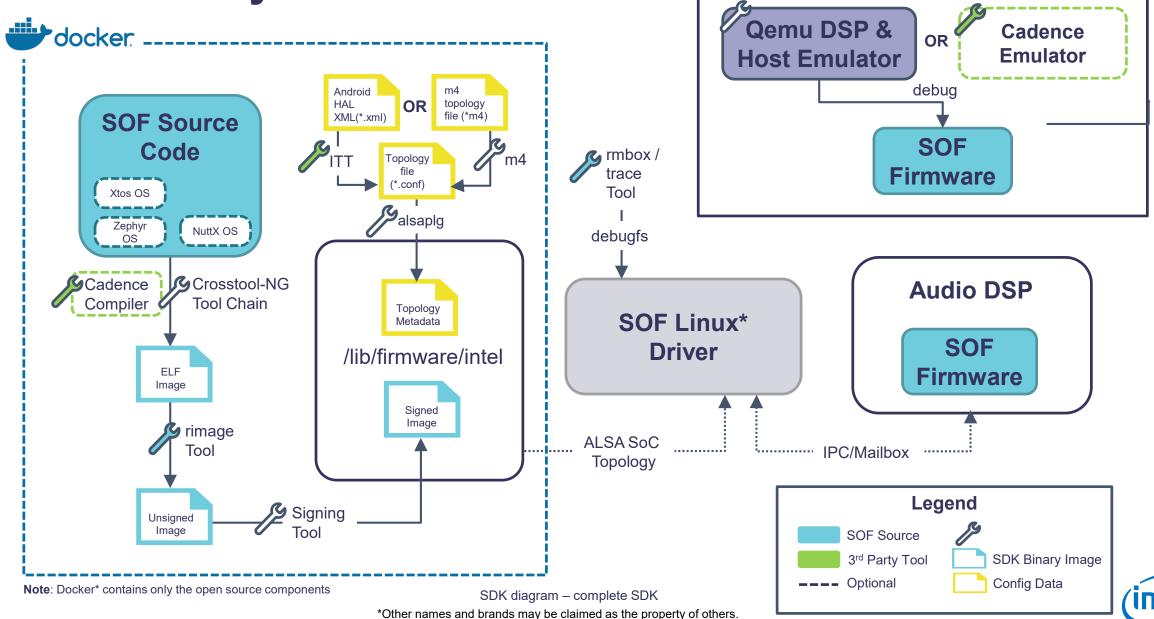

# **SDK Birds Eye View 1**

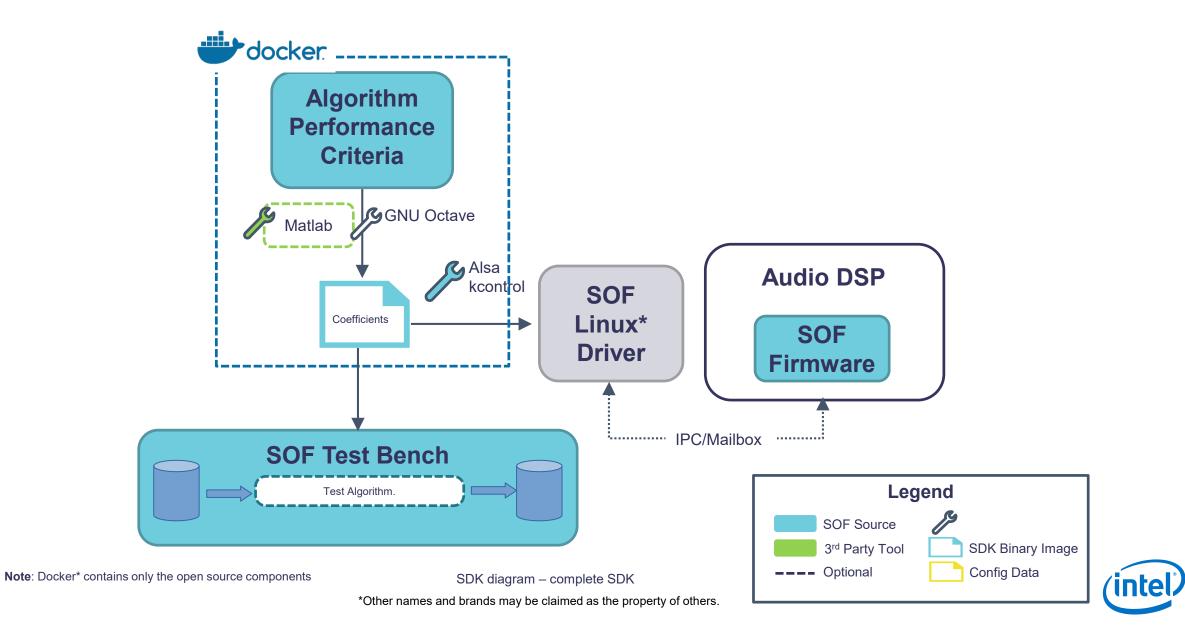

# **SDK Birds Eye View 2**

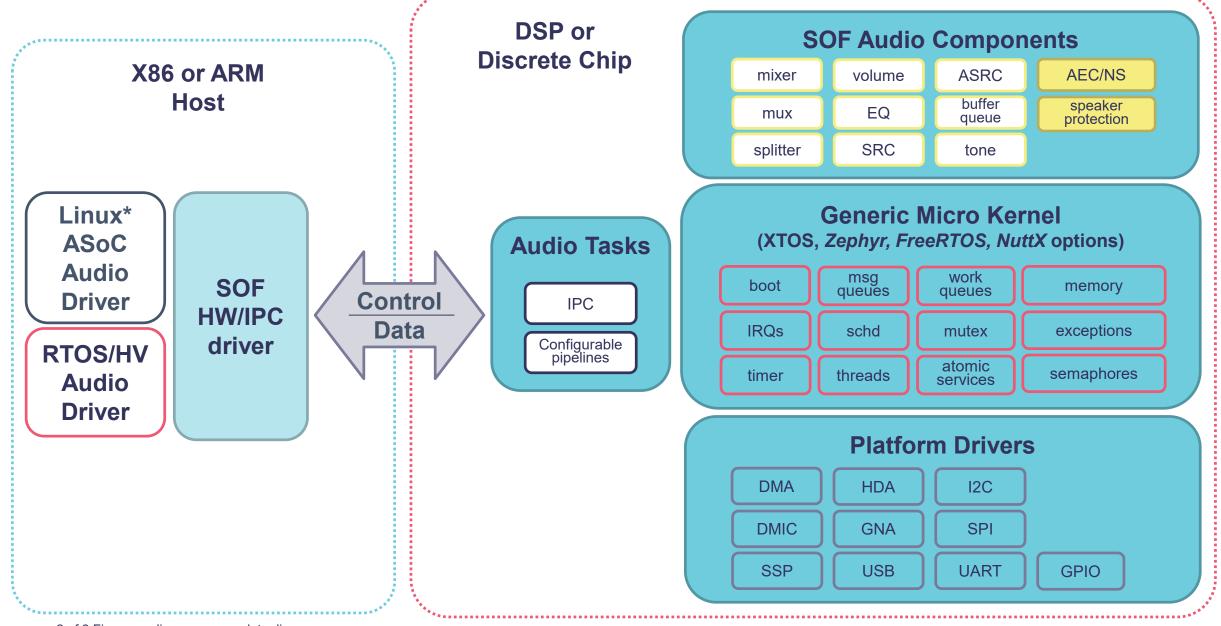

## **Firmware Overview**

- Architecture agnostic implementation in C with some assembler.

- Permissive BSD/MIT licensed code.

- Build time selection of features based on target (moving to use Kconfig).

- Scales down to ~40kB footprint (text, data and bss).

- Support for user defined audio processing pipeline topologies.

- Dynamically loaded pipelines at runtime.

- Statically stitched into image for host less operation.

- Allow general compute and signal processing. Not just an audio FW.

- Image generation tools provided to:

- Convert ELF to device specific firmware image formats.

- Sign firmware images with PKCS#1.5

#### **Firmware Architecture**

2 of 2 Firmware diagram - complete diagram

\*Other names and brands may be claimed as the property of others.

## **Driver Overview**

- Architecture agnostic.

- Dual GPL/BSD licensed code.

- Hardware and physical IO abstraction, so can work equally well with local MMIO and remote SPI based DSPs.

- Supports virtualization through VirtIO backend and frontends (using ACRN\*).

- Driver has no hard coded assumptions about DSP pipelines or components.

- Topologies loaded from FS.

- Component configurations can be runtime updated via ALSA kcontrols.

#### **Driver Architecture**

| ASoC I<br>codec<br>integration              | board<br>board                           | Driver<br>HW config |   |                   | •                          |

|---------------------------------------------|------------------------------------------|---------------------|---|-------------------|----------------------------|

| ASoC<br>topology                            | PCMs                                     | iver<br>Kcontrols   |   | IPC<br>Audio Data | DSP or<br>Discrete<br>Chip |

| <b>Gene</b><br>mixer                        | <b>ric IPC D</b> i<br>stream<br>pipeline | r <b>iver</b><br>PM |   |                   |                            |

| DSP Platform Driver<br>doorbell mailbox IRQ |                                          |                     |   |                   | er can currently be        |

| code loader                                 | 10                                       | РМ                  | ) | '`                | ا<br>*                     |

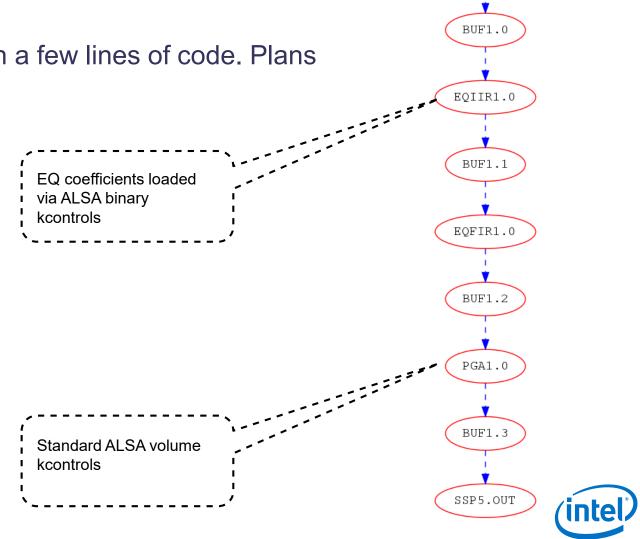

# **Pipeline Architecture**

- A pipeline is a set of audio processing components and buffers that share common scheduling.

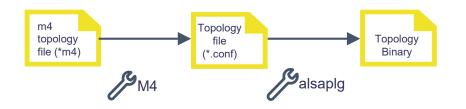

- Pipelines can currently be defined using M4 in a few lines of code. Plans for GUI.

Passthrough Playback 0

PCMOP

# **Continuous Integration - Oday**

#### **SOF Platforms**

| Vendor  | Platform                               | DSP                | Status                                               |

|---------|----------------------------------------|--------------------|------------------------------------------------------|

| Generic | Host PC                                | Host PC            | Testbench.                                           |

| Qemu    | Host PC                                | Qemu targets       | Currently only has support for xtensa based devices. |

| Intel   | Baytrail,<br>Cherrytrail,<br>Brasswell | 1 * Xtensa HiFi2EP | Upstream, support for upto 6 I2S DAIs.               |

| Intel   | Haswell,<br>Broadwell                  | 1 * Xtensa HiFi2EP | Upstream, need I2S integration for some codecs.      |

| Intel   | Apollolake,<br>Geminilake              | 2 * Xtensa HiFi3   | Upstream, support for I2S, DMIC, HDMI and HDA.       |

| Intel   | Cannonlake,<br>Whiskylake              | 4 * Xtensa Hifi4   | Upstream, support for I2S, DMIC, HDMI and HDA.       |

| Intel   | Suecreek HAT<br>on Rasberry PI         | 2 * Xtensa HiFi4   | Upstream core, boot over SPI WiP.                    |

| Xiaomi  | ARM M4                                 | CEVA Teaklite DSP  | Upstreaming WiP.                                     |

# **SOF Processing Components (open source)**

| Name   | Generic C<br>available | SIMD support         | Status                                                                                                                                        |

|--------|------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Volume | Yes                    | Xtensa HiFiEP, HiFi3 | Upstream, can process 1 – 8 channels, 16, 24 and 32bit formats.                                                                               |

| SRC    | Yes                    | Xtensa HiFiEP, HiFi3 | Upstream. 24 and 32bit formats. FIR polyphase<br>optimized M/N and M/N x O/P fractional rate<br>conversions.<br>Configuration tools upstream. |

| FIR    | Yes                    | Xtensa HiFiEP, HiFi3 | 16/24/32 bit formats, up to 192 taps.<br>Configuration tools upstream.                                                                        |

| IIR    | Yes                    | Planned              | 16/24/32 bit formats, up to 11 biquads or 22th order.<br>Configuration tools upstream.                                                        |

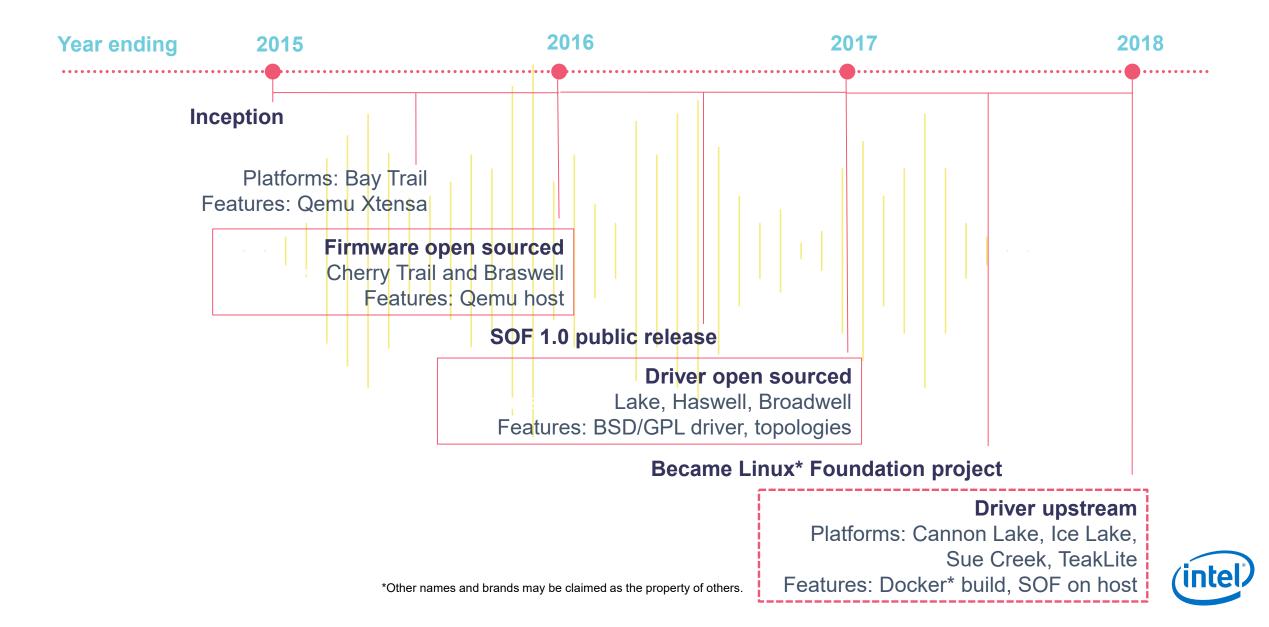

# **History**

#### **SOF Future Plans**

| Feature                         | Status                                                                      |  |

|---------------------------------|-----------------------------------------------------------------------------|--|

| GDB stub and tunnel.            | Initial firmware and kernel code in developer repository. Upstream in 2019. |  |

| RPMSG                           | Code complete, now upstreaming to SOF and Linux.*                           |  |

| Loadable<br>firmware modules    | Initial code in github, still WiP. Upstream in 2019.                        |  |

| CMSIS RTOS<br>Abstraction layer | Work in progress.                                                           |  |

## **Supporting Organizations**

#### **Firmware Preference**

- Linux\* already has a preference for open source drivers over closed source drivers.

- Should this preference also be extended to open source firmware in the future?

- Selection criteria would also have to consider:

- Features.

- Stability.

- Portability.

- Some open source firmware could still contain binary blobs.

- Regulatory reasons (e.g. comply with FCC regulations).

- 3rd party IP (e.g. some audio processing algorithms).

#### **Q & A**

## www.sofproject.com https://github.com/thesofproject

Visit the booth for demo.

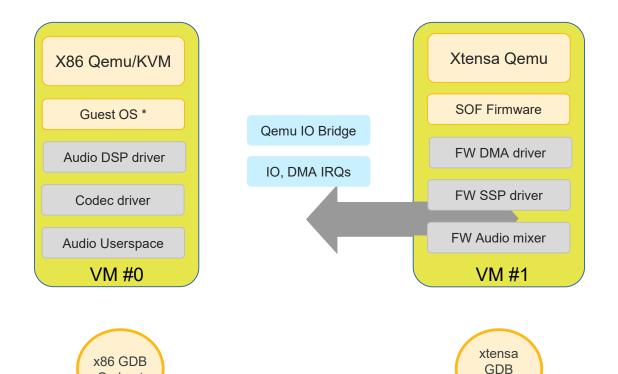

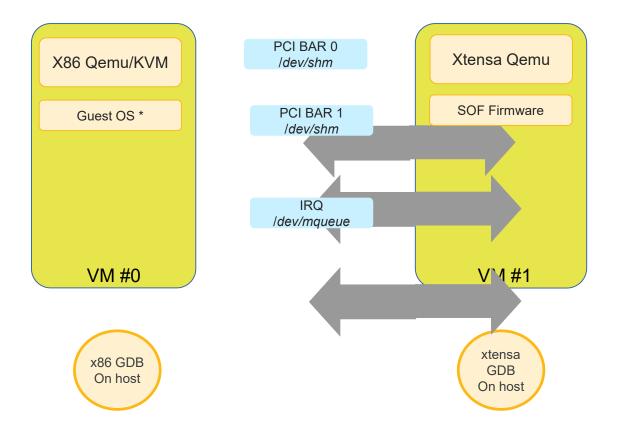

Qemu Heterogeneous Virtualization

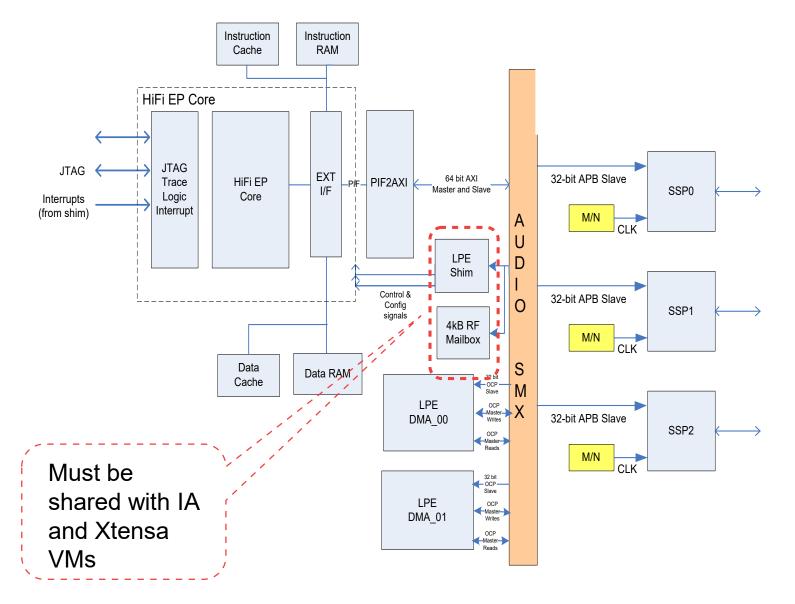

# **Baytrail DSP Architecture**

- Xtensa HiFi 2EP core

- 96kB Instruction RAM

- 168kB Data RAM

- 2 \* DMACs

- 3 \* I2S ports

- PCI device from host OS

- Firmware and host share

- SHIM registers

- Mailbox memory

# **Heterogeneous Virtualization**

On host

On host

- Firmware must be debugged alongside driver.

- Qemu used to virtualize drivers and firmware together.

- Host side almost real time.

- DSP side emulated.

# **Heterogeneous IO bridging**

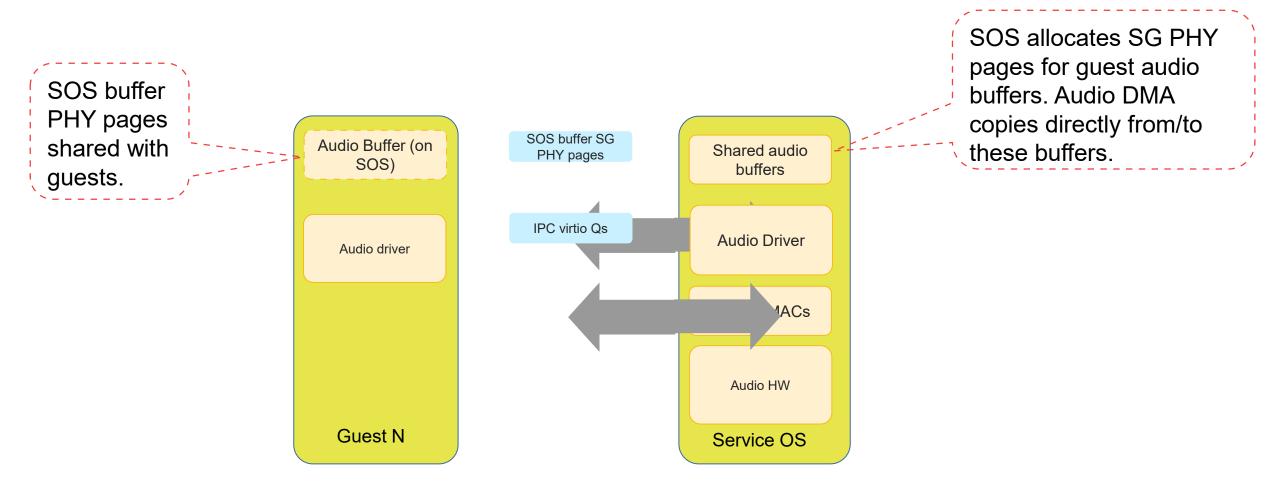

# **Zero Copy Virtual Audio**

# **Zero Copy Audio Virtualization**

# Legal notices and disclaimers

- This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest forecast, schedule, specifications and roadmaps.

- Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at intel.com, or from the OEM or retailer. No computer system can be absolutely secure.

- Tests document performance of components on a particular test, in specific systems. Differences in hardware, software, or configuration will affect actual performance. Consult other sources of information to evaluate performance as you consider your purchase. For more complete information about performance and benchmark results, visit <u>http://www.intel.com/performance</u>.

- Cost reduction scenarios described are intended as examples of how a given Intel-based product, in the specified circumstances and configurations, may affect future costs and provide cost savings. Circumstances will vary. Intel does not guarantee any costs or cost reduction.

- Statements in this document that refer to Intel's plans and expectations for the quarter, the year, and the future, are forwardlooking statements that involve a number of risks and uncertainties. A detailed discussion of the factors that could affect Intel's results and plans is included in Intel's SEC filings, including the annual report on Form 10-K.

- The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

- No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

- Intel does not control or audit third-party benchmark data or the web sites referenced in this document. You should visit the referenced web site and confirm whether referenced data are accurate.

- Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others.

© 2018 Intel Corporation.